# A New LLR based MPE-FEC Decoding Algorithm

Taedoo Park\*, Minhyuk Kim\* and Jiwon Jung\*

\* Dept. of Radio Science Engineering, Korea Maritime University, Dongsam-dong, Yeongdo-Gu, Korea Maritime University, Busan 606-791, Korea

bokddori@hhu.ac.kr

#### Abstract

In digital video broadcasting-handhelds (DVB-H), the contents to be transmitted come in the form of internet protocol (IP) datagram, which are passed to the multi-protocol encapsulation with forward error correction (MPE-FEC) entity. MPE-FEC employs erasure Reed-Solomon (eRS) error correction combined with cyclic redundancy check (CRC), is defined in standard. However, a critical factor must be considered when dealing with a longterm fading channel. If there is only one bit error in an IP packet, the entire IP packet is considered unreliable, even if it contains many correct bytes. To mitigate this effect, this paper proposed hybrid decoding algorithm using the log likelihood ratio (LLR) values. By simulation we show that the performance of the proposed decoding algorithm is superior to that of conventional one.

Keywords: MPE-FEC, DVB-H, IP packet, eRS codes, LDPC codes, LLR

### **1. Introduction**

The DVB-H provide an efficient way to convey multimedia IP services over digital terrestrial broadcasting networks towards mobile wireless handhelds. The DVB-H standard, MPE-FEC includes eRS, combined with virtual interleaving, to compensate for a long-term fading environment [1]. Several enhancements and modifications are under consideration, including adopting strong error correction codes and longer interleaving methods to compensate for long-term fading events in mobile environments. The DVB forums are currently working to define a new hybrid satellite/terrestrial delivery system in order to provide satellite services to portable devices. They recommend eRS codes as upper layer coding method and low density parity check (LDPC) codes specified in DVB-S2 as physical layer coding method. The advantage of eRS is that it is capable of correcting more erroneous code symbols than the conventional RS codes. The erasure information can be obtained from CRC error detection [2]. However, a critical factor must be considered when dealing with a long-term fading channel [3]. In fact, at the end of every MPE-FEC section, there is a CRC-32 field calculated over the entire section, to detect erroneous sections at the receiver side. If there is only one bit error in an IP packet, the entire IP packet is considered as unreliable bytes, even if it contains correct bytes. This implies that if there is one byte error in an IP packet of 512 bytes, 511 correct bytes are erased from the frame. In this paper, based on the physical layer coding method with LDPC codes, a new MPE-FEC decoding algorithm is proposed in this paper. At the receiver side, the erasure information is obtained directly from LLR from the bit node information of LDPC decoder, rather than the CRC information. Base on erasure information obtained from LLR value, this paper proposed a new hybrid MPE-FEC decoding algorithm. In this algorithm, if the number of erased bytes is less than the error correction capability, an eRS codes is used, otherwise, a conventional decoder that buffers another received symbol memory is used. The main difference between the two decoding methods analyzed in this paper is the manner in which the erasure information is obtained and how this information is utilized. Furthermore, the performance of the proposed decoding algorithms is investigated in terms of interleaving size and IP packet size.

## 2. Conventional MPE-FEC Encoding Algorithms

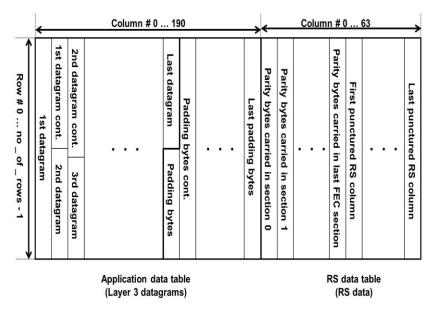

In this paper, we used eRS(255,191,64) with rate of 3/4 as MPE-FEC coding method. Therefore the MPE–FEC frame is arranged as a matrix with 255 columns and a variable number of rows, as shown in Figure 1. The maximum number of rows is 1024, which results in a total MPE–FEC frame size of almost 2 Mbits, as each element in the matrix contains one byte of information. The possible number of rows is 256, 512, 768 and 1024. The left-hand component of the MPE–FEC frame, consisting of the first 191 columns, is dedicated to the IP datagram and possible padding, and it is called the application data table. The right-hand component of the MPE–FEC frame, consisting of the 64 remaining columns, is dedicated to the parity information of the FEC codes, and it is called the RS data table. After all datagram fill in the application data table, any unfilled byte positions are padded with zeros. Then, for each row, the 64 parity bytes from the 191 bytes of data are calculated. Finally the data are transmitted in columns. The procedures of an interleaving and de-interleaving process are same on the data respectively before and after the RS coding, and are generally indicated as "virtual interleaving" [5].

Figure 1. Structure of MPE-FEC Memory

When the decoder begins to receive data, it has an empty MPE-FEC frame structure, with all byte elements marked as unreliable. Since the byte element address is indicated in the header of every received section, the receiver can store the received datagram in the correct byte element of the application data table or RS data table. CRC-32, which detects erroneous sections, marks these positions as reliable or unreliable. All empty elements of the MPE-FEC frame remain as unreliable bytes. If the MPE-FEC sections are received, the receiver introduces the number of padding bytes in the application data table, as indicated in the MPE-FEC sections. It marks these padding bytes as reliable. If the receiver does not receive the last

MPE section correctly, it assumes that all byte elements between the last correctly received section and the first padding column constitute lost data, and it is marked as unreliable. With this reliability information, the eRS decoder can correct up to 64 such bytes per 255 byte code word. It should be noted that any 64 bytes can be corrected, *i.e.*, it does not matter whether one bit or all eight bits are in error. If there are more than 64 unreliable byte elements in a row, the RS decoder cannot make any corrections, and it merely outputs the bytes, without error correction.

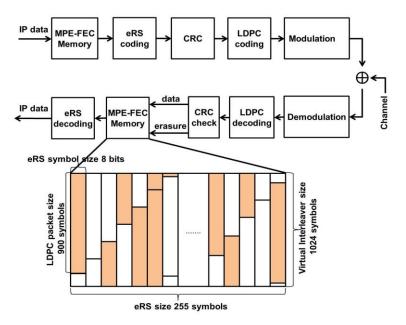

Figure 2 shows the structure of the conventional MPE-FEC using the CRC-based eRS decoding algorithm.

Figure 2. MPE-FEC Memory based on the CRC Method

For transmission, the frame is divided into sections, so that the IP datagram constitutes the payload of a MPE section and the redundancy column constitutes the payload of the MPE-FEC section. After the section header is attached, the CRC-32 redundancy bytes are calculated for the section. The sections are transmitted in the MPEG-2 transport stream (TS) format defined in the Reference [4]. The output of the physical layer, *i.e.*, the LDPC decoding output, consists of TS packets that are input to the upper layer IP decapsulator. After the CRC-32 check on the erroneous sections, the IP datagram is considered as unreliable bytes, and the IP datagram is erased. The erased IP datagram are depicted as black boxes in Figure 2.

### 3. Proposed MPE-FEC Decoding Algorithm

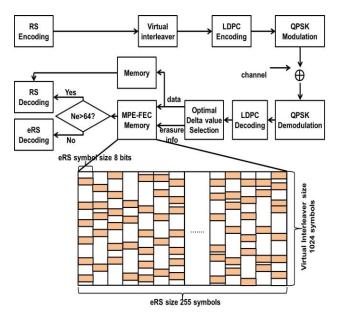

As described in the previous Section, the erasure information can be obtained from CRC error detection. However, a critical factor must be considered when dealing with a long-term fading channel such as Reference [3]. In fact, at the end of every MPE-FEC section, there is a CRC-32 field calculated over the entire section, to detect erroneous sections at the receiver side. If there is only one bit error within the IP packet, the entire IP packet is considered as unreliable bytes, even if it contains correct bytes. In order to solve the problem, this paper proposed a new simple hybrid MPE-FEC decoding algorithm using the erasure information

obtained from LLR of physical layer decoding, as shown in Figure 3. Therefore the unit of erasure information is not an IP packet unit but each symbol within an IP packet.

Figure 3. Structure of Hybrid MPE-FEC Method

In the LDPC decoding, final information of LDPC decoding is bit node information [6]. Upon receiving symbols, the check nodes make use of the parity check equations to update the bit node information and send it back. After finishing final iterations, soft values of bit node information are sent to eRS decoder and erasure information are obtained from this information. In terms of performance and complexity measures, we find an optimal criterion of discarding unreliable symbols. It is very important to decide how the erasure information can be obtained. Let us denote the erasure decision threshold  $\delta$  may be defined as Equation (1).

If,

$$|v_n| \ge \delta$$

, not erased

If,  $|v_n| < \delta$ , erased (1)

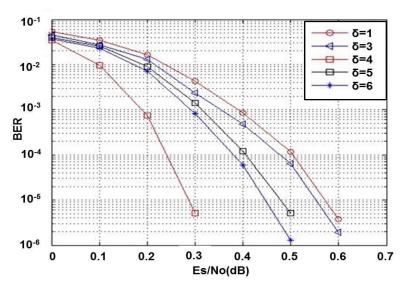

Where vn means soft value of bit node information after the LDPC decoding, However, it is very important to decide the  $\delta$ ; if it is too high, the total number of erasures would exceeds the maximum error correction capability; if it is too low, the probability of the error correction would be low. Therefore, we decide the  $\delta$  using the computer simulation by trialan-errors. As shown in Figure 4, we simulated the various values of  $\delta$  from one to six. The simulation result shows the optimal value of  $\delta$  is four. In next step, we check the how many erasure bytes are contained in the 255 bytes column. The Ne means the number of erasure bytes that are unreliable bytes after check the threshold. If Ne is less than the error correction capability, the eRS decoding is applied, otherwise, conventional RS decoding is applied using the additional memory obtained from LDPC decoder. The reason for using conventional RS decoding is to prevent correct symbols from being erased. This proposed algorithm is very simple, and it avoids additional hardware and modification of the standard. It doesn't need to calculate a CRC process and it prevents one bit error from resulting in an IP packet erasure.

Figure 4. Performance of Hybrid MPE-FEC Method According to  $\delta$

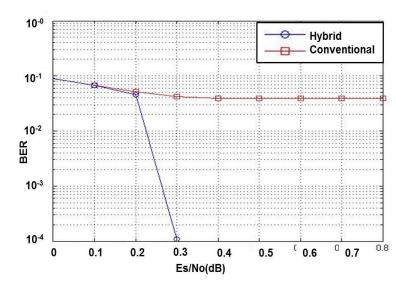

Figure 5 shows the BER performance comparison between the conventional MPE-FEC method and the new hybrid MPE-FEC method in the long term fading channel. The word "Conventional" in Figures means the CRC based algorithm depicted in Figure 2. To compare the performance of conventional decoding methods and proposed one, we used eRS(255,191,64) with rate of 3/4, half rate LDPC codes with block size of 64800 described in [4], and IP packet size of 1024 bytes. The channel models used in the simulator were long term fading channel [3].

In the long term fading channel, the conventional scheme doesn't correct erroneous received bits. This is why the erased bytes include numerous correct bytes, and it exceeds the error correction capability. Therefore, the proposed hybrid decoding algorithm has a superior performance compared to the conventional algorithm in the long term fading channel.

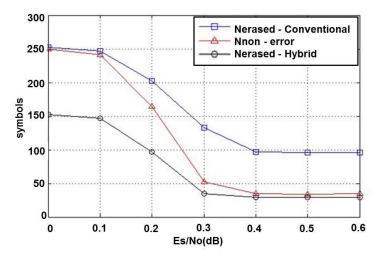

In addition, to analyze the result of the Figure 5, we need to investigate the how many nonerror symbols are considered as unreliable. Figure 6 shows the average number of non-error symbols within unreliable symbols in MPE-FEC memory.

$$N_{erased} = N_{non-error} + N_{real-error}$$

(2)

For example, at the value of Es/No is 0.3, among the total 255 erased symbols, 135 symbols are non-error symbols in conventional method and 55 symbols are non-error symbols in proposed algorithm. In conventional method, since just one bit error in an IP packet, the entire IP packet is considered as erased symbols, this causes error flooring in eRS decoding as shown in Figure 5. We can see the expected behavior of proposed algorithm of MPE-FEC decoding prevent correct symbols from being erased.

International Journal of Multimedia and Ubiquitous Engineering Vol. 8, No. 4, July, 2013

Figure 5. Performance Comparison in Long Term Fading Channel

Figure 6. Average Number of Non-error Symbols within Erased Symbols in MPE-FEC Memory

### 4. Simulation Results

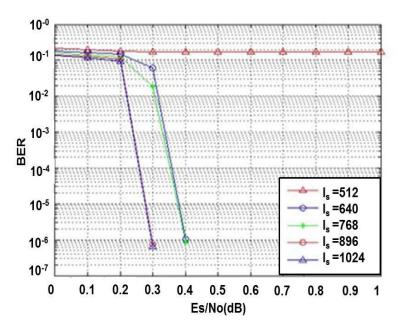

From the Figure 3, Figure 7 shows the performance of hybrid MPE-FEC by increasing the virtual interleaving size, Is. The interleaving size, that is the number of bytes in the frame, can be one of 255, 512, 768 or 1024. As to the virtual interleaving size, a smaller size is more susceptible to the blockage impairment in long term fading channel.

Figure 7. Performance of Hybrid MPE-FEC for Various Interleaving Size

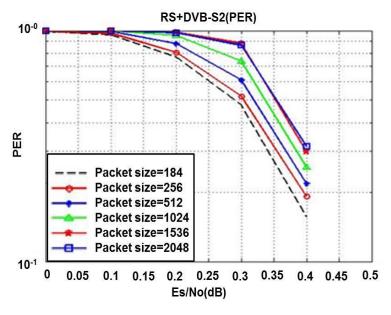

Figure 8 shows the packet error rate (PER) performance for various IP packet sizes. IP packet size is the same as the size of datagram shown in Figure 1 Fixed on Is=1024 bytes, we observe that the smaller IP packet size, the better the performance. This is because a smaller packet size is not affected by the number of erased bytes. Since the gain between different IP packet size is almost 0.05 dB, we conclude that the IP packet size is not much affected to PER performance.

Figure 8. PER Performance for Various IP Packet Sizes

## **5.** Conclusions

In this paper, we proposed a new decoding algorithm for a terrestrial delivery system defined in the DVB-H standard and addressed some limitations in the conventional CRC-32 based decoding algorithm. In the conventional CRC-32-based decoding algorithm, a single bit error causes the entire IP packet to be considered unreliable, even if it contains many correct bytes. This causes the performance degradation in a long-term fading channel. Therefore, this paper proposed a new upper layer decoding methods combined LLR-based erase detect and hybrid decoding. After LDPC decoding, erasure information is obtained from soft outputs of LDPC decoder. This approach only uses the LLR value and avoids CRC-32 calculation. The unit of erasure information is not an IP packet but a symbol within an IP packet, thereby improving the error correction ability. After detect the erased symbol by LLR values, we apply both conventional RS decoding and an eRS decoding algorithm, based on whether the number of erasure bytes is greater than or less than the error correction capability. Computer simulations show that the hybrid decoding algorithm achieves a coding gain compare to conventional MPE-FEC decoding algorithm in the long term fading channel. Furthermore, we observe that virtual interleaving is a crucial component for improving the performance in a long-term fading channel. In addition, we concluded the larger the virtual interleaving size, and the smaller the IP packet size, the better the performance.

### Acknowledgements

This work was supported by Defense Acquisition Program Administration and Agency for Defense Development under the contract UD100002KD and supported by the MKE(The Ministry of Knowledge Economy), Korea, under the ITRC(Information Technology Research Center) support program supervised by the NIPA(National IT Industry Promotion Agency)(NIPA-2011-C1090-1121-0007).

## References

- [1] G. Faria, J. A. Henriksson, E. Stare and P. Talmola, "DVB-H: Digital Broadcast Services to Handheld Devices", Proceedings of the IEEE, vol. 94, no. 1, (2006) January.

- [2] T. Jokela, J. Paavola, H. Himmanen and V. Ipatov, Editors, "Performance Analysis of Difference Reed-Solomon Erasure Decoding Strategies at the DVB-H Link Layer", Proceedings of the 17th Annual IEEE International Symposium on Personal, Indoor and Mobile Radio Communications, (2006) September 11-14; Helsinki, Finland.

- [3] V. Schena and F. Ceprani, Editors, "A satellite network for train environment in the FIFTH Demonstration", Proceedings of the IST Mobile & Wireless Telecommunication Summit 2003, (2003) June 15 ~ 18; Aveiro, Portugal.

- [4] ETSI EN 301 210: "Digital Video Broadcasting (DVB): Framing Structure, Channel Coding and Modulation for Digital Satellite News Gathering (DSNG) and Other Contribution Applications by Satellite", (DVB-S2), (2005) March.

- [5] J. Paavola, H. Himmanen, T. Jokela, J. Poikonen, and V. Ipatov, "Performance Analysis of MPE-FEC Decoding Methods at the DVB-H Link Layer for Efficient IP Packet Retrieval", IEEE TRANSACTIONS BROADCASTING, vol. 35, no. 1, (2007) March, pp.263-275.

- [6] D. J. C. Mackay and R. M. Neal, "Near Shannon Limit Performance of Low-Density Parity-Check Codes", Electronics Letter, vol.32, (1996) August, pp. 1645-1646.

## Authors

**Taedoo Park** received his BS and MS degrees from Korea Maritime University, Busan, Korea in 2008 and 2010, respectively, all in Radio Science Engineering. He is in Kore Maritime Graduate University. His research interests are channel coding, digital modem and FPGA design technology.

**Minhyuk Kim** received his BS, MS, and PhD degrees from Korea Maritime University, Busan, Korea in 2006, 2008 and 2012, respectively, all in Radio Science Engineering. Since 2012, he has been with the ETRI. His research interests are channel coding, digital modem and FPGA design technology.

**Jiwon Jung** received his BS, MS, and PhD degrees from Sungkyunkwan University, Seoul, Korea, in 1989, 1991, and 1995, respectively, all in electronics engineering. From November 1990 to February 1992, he was with the LG Research Center, Anyang, Korea. From September 1995 to August 1996, he was with Korea Telecom (KT). From August 2001 to July 2002, he was an Invited Researcher with the Communication Research Center Canada [supported by Natural Sciences and Engineering Research Council of Canada (NSERC)]. Since 1996, he has been with the Department of Radio Science and Engineering, Korea Maritime University, Busan, Korea. His research interests are channel coding, digital modem, field programmable gate-array (FPGA) design technology, and digital broadcasting systems. International Journal of Multimedia and Ubiquitous Engineering Vol. 8, No. 4, July, 2013