# A Novel Low Power and Low Voltage Bulk-Input Four-Quadrant Analog Multiplier in Voltage Mode

Sheema Soltany and Abdalhossein Rezai

ACECR- Institute of higher education, Isfahan, Iran Sh.soltani66@gmail.com Academic Center for Education, Culture and Research (ACECR), Isfahan University of Technology (IUT) branch, Isfahan, Iran rezaie@acacr.ac.ir

#### Abstract

This paper presents a new CMOS four-quadrant low voltage and low power analog multiplier circuit in voltage mode. In the proposed analog multiplier, transistors are biased in weak inversion by driving them at bulk terminals. The proposed design has fully differential ended output. Input signal ranges are  $\pm 40$ mV and all transistors have the equal sizes. Simulation results have been presented by HSPICE simulator in 0.18µm standard CMOS technology to confirm the operation of the circuit. The results show that the proposed analog multiplier has several advantages in comparison with other analog multipliers.

**Keywords**: analog multiplier, voltage mode, bulk-input CMOS circuits, four-quadrant, weak inversion

#### 1. Introduction

Analog multipliers are coming into account as essential and necessary circuit elements. Multiplier is a device having two analog inputs and one output. Output signal is the multiplied result of the inputs [1]. There is many different types of multipliers related to their input mode (currents [1-4] or voltages [5-8] or a mixture of them [9-10]) and the region of the operation (saturation [11-12, 4], linear [13, 5] and weak inversion [2, 7-8, 14]). Analog multiplication can be applied in many applications such as adaptive filters, frequency doublers, equalizer, modulators, automatic gain controlling, artificial neural networks [5, 15-17], image processing, medical treatments [9], in sensor applications [10] and fuzzy logic controllers. These days, the electronic society is faced with orders in relation to low power dissipations [3, 17].

Primary circuits were reported first in Gilbert works using BJT transistors [18]. Moreover, many works have been proposed including different types of four-quadrant multiplier circuits for low power applications even digital [19]. There are many modes for managing an analog multiplier according to multiplier types. In all these works a practical way for obtaining a low power dissipation topology is to use MOSFETs in weak inversion layer [2, 7-8, 14]. Another way is to drive them in bulk terminals [14]. As a result, we need an efficient structure for analog multiplier. Figure 1 shows a simple diagram of multiplication.

Figure 1. A Simple Diagram of Multiplication

The main reason for choosing this structure is answering many desires that were not acceptable and available in many ones such as [12]. In [12], the most noticeable factor is the power consumption which is  $32\mu$ W. However, this is considerable. The main reason for achieving these high levels power consumption is utilizing more transistors. For the same reason papers [2,4,20] and [21] have high power consumption.

The authors of [12] proposed a low power CMOS analog multiplier using 13 transistors. All of them have been driven in the linear region using  $0.35\mu m$  CMOS technology. In [12], W/L is  $0.8\mu m/0.35\mu m$ , input signals are X=0.5V, Y=1.5V and supply voltage is 1.5V, which is ten times bigger than V<sub>DD</sub> in this design and finally the power consumption is  $32\mu W$ . The power consumption in this paper is also high.

Gravati *et al.* [2] proposed a novel current mode very low power analog CMOS fourquadrant multiplier. The Gravati *et al.* analog multiplier [2] consist of 14 transistors. Moreover, they using 0.35 $\mu$ m technology. MOSFETs are in weak inversion region with 2V supply voltage and 250nA bias current. The maximum power consumption reported by Gravati *et al.* [2] is 5.5 $\mu$ W. Although the transistors work in weak inversion, but it is not in a very low power structure. It may have been caused due to large number of transistors and high level V<sub>DD</sub> and I<sub>BIAS</sub>.

Beyraghi *et al.* [4] proposed a current mode four-quadrant analog multiplier designed in 0.35  $\mu$ m CMOS Technology using 20 saturated transistors. The utilized supply voltage is  $\pm 1.5$ V and input current range is  $\pm 10\mu$ A. Aspect ratio of transistors are in different size. The reported power dissipation in [4] is 475  $\mu$ W. The main reasons for this power consumption could be large numbers of MOSFETs and high amount of supply voltage. Although the process number and driving region are also noticeable.

In [20], there is a design of four-quadrant analog multiplier consist of a multiplier cell. It has 12 transistors working in saturation. CMOS Technology is  $0.5\mu m$  with W=1 $\mu m$  and L=2 $\mu m$ . The input range is 200mV for both inputs, supply voltage is 2.5V and bias current is 10nA. The power dissipation is not mentioned, but it is certainly clear that it is a high value, because of using high input ranges and many number of MOSFETs.

Popa [21] scrutinized two current mode multiplier topologies including 17 and 23 transistors. The process is 0.18 $\mu$ m CMOS technology with 1.2V supply voltage and 300 $\mu$ A range for inputs in saturation region. The simulation results for both circuits show the power consumption of 60 $\mu$ W and 75 $\mu$ W, respectively. The author has claimed the circuits use the small value of minimal supply voltage and the power consumption is extremely low, however it could be even lower.

In this paper, a CMOS low power four-quadrant analog multiplier has been presented with only 8 MOSFETs. The transistors are biased in weak inversion using  $0.18\mu m$  CMOS Technology. Supply voltage is 0.15V and bias current equals to 10nA. The input ranges are  $\pm 40mV$ . We use differential inputs and we also have differential outputs. As effective inversion layer in pMOS devices increases by negative potential of n-type bulk with respect to p-type source, there would be an exponential relationship between drain to source current and bulk to source voltage. The proposed multiplier is simulated in HSPICE. The simulation results show that the power consumption in the proposed analog multiplier is 444.5pW.

The rest of this paper is organized as follows: Section 2 described circuit explanation. Section 3 presents the mismatch of the proposed multiplier. Simulation results are presented in Section 4. Finally, the paper is concluded in section 5.

## 2. Explanation of the Proposed Circuit

With respect to the operation of a MOS device in weak inversion, relative equations are as follows:

$$I_{DS} = I_{D0} e^{\frac{-V_{gs}}{\eta U_T}} e^{\frac{-(\eta - 1)V_{bs}}{\eta U_T}} \left[ 1 - e^{\frac{-V_{ds}}{\eta U_T}} \right]$$

(1)

Eq. 1 is the drain to source current of MOS (ignoring the early effects VDS<<VE) [22, 23], where  $I_{D0} = I_s e^{\frac{V_{TH}}{\eta U_T}}$ ,  $I_s = 2\eta\beta U_T^2$ ,  $U_T = \frac{\kappa_T}{q}\eta$  is the sub-threshold slope factor and is between 1 and 2 [22, 24],  $\beta = \mu C_{ox} \frac{W}{L} V_{E}$ , and  $V_E$  is the early voltage that is nearly 10 V.

As explained above, the devices must operate in weak inversion, below  $V_{TH}$ , and bulk has voltage, then  $V_{sb}$  has a considerable value [11], which is computed as follows:

$$V_{TH} = V_{TH0} + \gamma (\sqrt{|V_{SB} + \phi_0|} - \sqrt{|\phi_0|})$$

(2)

In this equation  $V_{TH} = V_{TH0}$  where  $V_{sb} = 0$ ,  $\phi_0 = 2\phi_F + \nabla \phi$ ,  $\nabla \phi = 6U_T$ , and  $\gamma$  is the body effect parameter that depends on the process and defines as follow:  $\gamma = \frac{-\sqrt{2q} \epsilon_{si} N_D}{C_{OX}}$ .

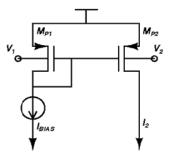

The exponential function in this topology defines as a current mirror which is biased in bulk terminals and is shown in Figure 2.

Figure 2. Exponential Circuit

The current equation for this circuit based on Eq. 1 can be written as follows:

$$I_{Ds1} = I_{D0} e^{\frac{-v_{gs1}}{\eta U_T}} e^{\frac{-(\eta - 1)v_{bs1}}{\eta U_T}}$$

(3)

$$I_{Ds2} = I_{D0} e^{\frac{-v_{gs2}}{\eta U_T}} e^{\frac{-(\eta - 1)v_{bs2}}{\eta U_T}}$$

(4)

$$I_{Ds2} = I_{BIAS} e^{\frac{-(\eta-1)(V_{bs2}-V_{bs1})}{\eta U_T}}$$

(5)

Where  $V_{sb2}$ ,  $V_{sb1}$  are very small  $(|V_{sb2}|, |V_{sb1}| \ll \frac{\eta U_T}{(\eta-1)}$ , with  $\eta = 1.2$ , so  $\frac{\eta U_T}{(\eta-1)} = 155 mv$ ), the equations are as follows, which result in more dynamic range in comparison to multipliers with gate inputs.

$$I_{Ds2} = I_{BIAS} e^{\frac{-(\eta-1)V_{bS2}}{\eta U_T}} e^{\frac{(\eta-1)V_{bS1}}{\eta U_T}}$$

(6)

According to Taylor's series:

$$I_{Ds2} = I_{BIAS} \left[ 1 - \left( \frac{(\eta - 1)V_{Ds2}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{Ds2}}{\eta U_T} \right)^2 - \cdots \right] \times \left[ 1 + \left( \frac{(\eta - 1)V_{Ds2}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{Ds2}}{\eta U_T} \right)^2 + \cdots \right]$$

(7)

We can consider these two equations as equal ones if  $|(\frac{(\eta-1)V_{DS2,1}}{\eta U_T})| \ll 1$ .

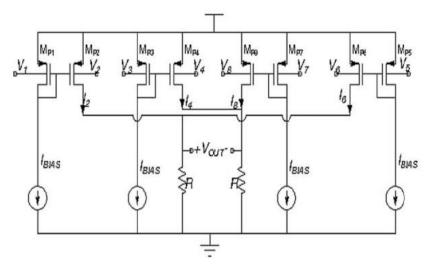

For presenting four-quadrant multiplier, we need four circuits as shown in Figure 2. Figure 3 shows a four-quadrant multiplier architecture. It should be noted that  $|V_{in2}|, |V_{in1}| \ll \frac{\eta U_T}{(\eta-1)}$ .

Figure 3. The Proposed Multiplier Topology

In Figure 3, assume  $V_{bs}$  of all eight pMOS devices are  $V_1, V_2, V_3, V_4, V_5, V_6, V_7$  and  $V_8$ . The input voltages are  $V_1 = V_7 = V_b + V_{in1}$ ,  $V_2 = V_4 = V_b - V_{in2}$ ,  $V_3 = V_5 = V_b - V_{in1}$ , and  $V_6 = V_8 = V_b + V_{in2}$ .

So, the currents in each branch is as follows:

$$I_{Ds2} = I_{BIAS} e^{\frac{-(\eta - 1)(V_2 - V_1)}{\eta U_T}} = I_{BIAS} e^{\frac{(\eta - 1)(V_{in2} + V_{in1})}{\eta U_T}}$$

(8)

In Eq. 8 we ignore the higher order terms to approach Eq. 9:

$$\cong I_{BIAS} \left[ 1 + \left( \frac{(\eta - 1)V_{in2}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{in2}}{\eta U_T} \right)^2 \right] \times \left[ 1 + \left( \frac{(\eta - 1)V_{in1}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{in1}}{\eta U_T} \right)^2 \right]$$

(9)

In the same way  $I_{Ds4}$ ,  $I_{Ds6}$ ,  $I_{Ds8}$  defines as below:

$$I_{Ds4} = I_{BIAS} e^{\frac{-(\eta-1)(V_4 - V_3)}{\eta U_T}} = I_{BIAS} e^{\frac{(\eta-1)(V_{in2} - V_{in1})}{\eta U_T}} \cong I_{BIAS} \left[1 + \left(\frac{(\eta-1)V_{in2}}{\eta U_T}\right) + \frac{1}{2!} \left(\frac{(\eta-1)V_{in1}}{\eta U_T}\right)^2\right] \times \left[1 - \left(\frac{(\eta-1)V_{in1}}{\eta U_T}\right) + \frac{1}{2!} \left(\frac{(\eta-1)V_{in1}}{\eta U_T}\right)^2\right]$$

(10)

$$\cong I_{BIAS} \left[ 1 - \left( \frac{(\eta - 1)V_{in2}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{in2}}{\eta U_T} \right)^2 \right] \times \left[ 1 - \left( \frac{(\eta - 1)V_{in1}}{\eta U_T} \right) + \frac{1}{2!} \left( \frac{(\eta - 1)V_{in1}}{\eta U_T} \right)^2 \right]$$

(11)

$$I_{DS4} = I_{BIAS} e^{\frac{-(\eta-1)(V_B - V_T)}{\eta U_T}} = I_{BIAS} e^{\frac{(\eta-1)(V_{In2} - V_{In1})}{\eta U_T}} \cong I_{BIAS} \left[1 - \left(\frac{(\eta-1)V_{In2}}{\eta U_T}\right) + \frac{1}{2!} \left(\frac{(\eta-1)V_{In2}}{\eta U_T}\right)^2\right] \times \left[1 + \left(\frac{(\eta-1)V_{In1}}{\eta U_T}\right) + \frac{1}{2!} \left(\frac{(\eta-1)V_{In1}}{\eta U_T}\right)^2\right]$$

(12)

In this topology for multiplication  $I_{out}$  defines as  $I_{out} = (I_{Ds2} + I_{Ds2}) - (I_{Ds4} + I_{Ds8})$  and output voltage is as follows:

$$V_{out} = I_{out} \times R = [(I_{DS2} + I_{DS6}) - (I_{DS4} - I_{DS8})]R$$

(13)

So the output is as follows:

$$I_{out} \cong 4 \left[ \frac{(\eta - 1)}{\eta U_T} \right]^2 V_{in2} V_{in1} \tag{14}$$

As explained above inputs are differential named  $V_{in1}$  and  $V_{in2}$ . In first quadrant  $V_1$  is  $V_{in1}$  and  $V_2$  is  $V_{in2}$ . In other three quadrants  $V_3$ ,  $V_5$  and  $V_7$  are equal to  $V_{in1}$  and  $V_4$ ,  $V_6$  and  $V_8$  are equal to  $V_{in2}$ , respectively.

#### 3. Mismatch of the Proposed Multiplier

There would be some kind of mismatches between the devices because of the fabrication process, which is calculated by regarding to variations of process parameters and also the mismatch in the bias voltages or currents. The drain current may cause a mismatch due to  $I_{D0}$  including  $\beta$  mismatch (in weak inversion its effects can be neglected [24, 25]). Another factor, can be caused by  $V_{TH}$  that varies the current and the  $\eta$  due to bulk to source voltage,  $V_{BS}$ . For these mismatches we can consider a term as  $I_{D0}(1 + \Delta I_{D01})$  and bias mismatch can be considered as  $I_{BIAS} + \Delta I_{BIAS}$ . For each device in current mirror we assume another mismatch caused by  $V_{Ds}$  in output currents ( $I_{DS2}, I_{DS4}, I_{DS6}, I_{DS8}$ ) which introduces the factor  $\delta_{ij}$  where i and j refers to transistor pairs. So Eq. 1 can be rewrite as below:

$$I_{DS2} = I_{BIAS} \times \xi_{2,1} \times e^{-\frac{(\eta - 1)V_{bS2,1}}{\eta U_T}} \times \delta_{2,1}$$

(15)

Where  $\xi_{2,1} = \frac{(1+\Delta I_{D02})}{(1+\Delta I_{D01})}$  shows  $I_{D0}$  mismatch between  $M_{P1}$  and  $M_{P2}$  that their variations are ,  $\Delta I_{D02}$ , respectively,  $V_{bs2,1} = V_{bs2} - V_{bs1}$  and  $\delta_{2,1} = \left[1 - e^{-\frac{V_{ds2}}{\eta U_T}}\right] / \left[1 - e^{-\frac{V_{ds1}}{\eta U_T}}\right]$  is due to  $V_{abs}$  between the two pairs. As the input one applied to hull terminals as  $V_{abs} = V_{abs}$  and it is

to  $V_{ds}$  between the two pairs. As the inputs are applied to bulk terminals so  $V_{bs} = V_{in}$  and it is better to have only a parameter for mismatch factors like  $\rho$  so finally the Eq. 15 rewrites as:

International Journal of Multimedia and Ubiquitous Engineering V ol.11, No.1 (2016)

$$I_{DS2} = \rho_2 \times I_{BIAS} \times e^{\frac{(\eta - 1)(V_{in2} + V_{in1})}{\eta U_T}}$$

(16)

And  $\rho_2 = \xi_{2,1} \times \delta_{2,1}$ . Like this expression will be considered for other current equations, then we have:

$$I_{DS4} = \rho_4 \times I_{BIAS} \times e^{\frac{(\eta - 1)(V_{in2} - V_{in1})}{\eta U_T}}$$

(17)

$$I_{DS6} = \rho_6 \times I_{Bias} \times e^{\frac{-(\eta - 1)(V_{in2} + V_{in1})}{\eta U_T}}$$

(18)

$$I_{DS8} = \rho_8 \times I_{Bias} \times e^{\frac{-(\eta - 1)(V_{in2} - V_{in1})}{\eta U_T}}$$

(19)

With respect to Eq. 13 the summations are:

$$I_{DS2} + I_{DS6} = I_{Bias}(\rho + \Delta \rho_{2,6}) \left[ e^{\frac{(\eta - 1)(V_{in2} + V_{in1})}{\eta U_T}} - e^{\frac{-(\eta - 1)(V_{in2} + V_{in1})}{\eta U_T}} \right]$$

(20)

And

$$I_{DS4} - I_{DS8} = I_{Bias}(\rho + \Delta \rho_{4,8}) \left[ e^{\frac{(\eta - 1)(V_{in2} - V_{in1})}{\eta U_T}} - e^{\frac{-(\eta - 1)(V_{in2} - V_{in1})}{\eta U_T}} \right]$$

(21)

So final current equation presents as follows:

$$I_{out} \cong I_{Bias} \times \rho \times 4 \left[\frac{(\eta - 1)}{\eta U_T}\right]^2 V_{in2} V_{in1} + \lambda I_{Bias}$$

(22)

Where  $\lambda$  explains the mismatch due to multiplied part with  $\Delta \rho$ . The Eq. 22 shows the speculated expression for the mismatch process.

#### 4. Simulation Results

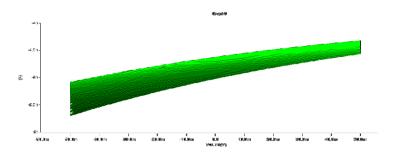

For taking the performance of the proposed multiplier, we have used  $0.18^{\mu m}$  CMOS technology in threshold voltage of -0.443 v, two identical resistant  $1M\Omega$ , 0.15V supply voltage, 10nA  $I_{BIAS}$  (to bias the transistors in weak inversion), equal size of the transistors (W/L,  $45^{\mu m}/2^{\mu m}$ ) and bias voltage  $V_b$  is 100mV. For DC characteristics Vin1 and Vin2 vary from -100 to 100mV. Figure 4 shows the DC simulations  $I_{out}$ -V<sub>in diff</sub>. Moreover, Differential input signals are shown in Figure 5. Table 1 shows the characteristic of the proposed multiplier. In Table 2, the results of the proposed analog multiplier are compared with other analog multipliers.

International Journal of Multimedia and Ubiquitous Engineering V ol.11, No.1 (2016)

Figure 4. DC Characteristic Iout-Vin diff

**Figure 5. Differential Input Signals**

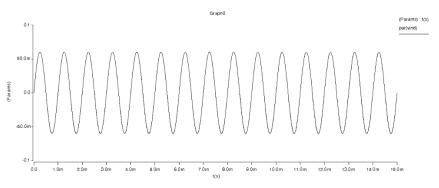

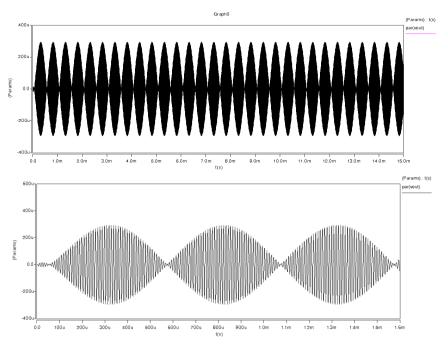

Transient response of the proposed analog multiplier circuit is shown in Figure 6, when two sinusoidal signals of 40mV and 30mV, in 10 and 100 KHz are applied to the inputs.

Figure 6. Transient Response of the Proposed Multiplier

| Parameters             | Result                     |  |  |

|------------------------|----------------------------|--|--|

| V <sub>DD</sub>        | 0.15 [V]                   |  |  |

| $\mathbf{V_b}$         | 100 [mV]                   |  |  |

| I <sub>BIAS</sub>      | 10 [nA]                    |  |  |

| Input dynamic<br>range | Vin1 30 [mV], Vin2 40 [mV] |  |  |

| POWER                  | 444.5 [pW]                 |  |  |

| Process used           | 0.18 [µm] CMOS             |  |  |

Table 1. Results of this Work

| Table 2. Comparison of Performance |

|------------------------------------|

|------------------------------------|

| Parameters  | This paper | [15]      | [25]       | [6]       |

|-------------|------------|-----------|------------|-----------|

| Process     | 0.18 [µm]  | 0.35 [µm] | 0.18 [µm]  | 0.35 [µm] |

| VDD         | 0.15 [V]   | 3.3 [V]   | 0.5 [V]    | 1.5 [V]   |

| Vb          | 100 [mV]   | NA        | 400 [mV]   | NA        |

| IBIAS       | 10 [nA]    | 10 [µA]   | 300 [nA]   | NA        |

| Input range | ±40 [mV]   | ±NA]      | ±80 [mV]   | ±120 [mV] |

| Power       | 444.5 [pW] | 0.34 [mW] | 714.3 [nW] | 6.7 [µW]  |

Table 2 performs a comparison between this paper and 3 other works. The circuit has used 0.18 $\mu$ m CMOS Technology. Based on our simulation results which are shown in Table 2, all parameters in this work are lower than the other ones. So the power consumption obviously will be in a lower range too. Power consumption are 0.34mW, 6.7 $\mu$ W and 714.3nW for [15], [6] and [25] respectively, but 444.5pW relates to this work.

## 5. Conclusion

A CMOS four-quadrant voltage mode analog multiplier circuit is presented which operates in weak inversion by driving it at bulk terminals. It is suitable for low power and low voltage applications as its power dissipation is 444.5pw. However the mismatch reduces its speed and output voltage range is very low. Circuit is designed in 0.18 $\mu$ m and the performance was simulated using HSPICE.

### References

- K. O. Tanno, Ishizuka and Z. Tang, "Four-quadrant CMOS current-mode multiplier independent of device parameters, Circuits and Systems II: Analog and Digital Signal Processing", IEEE Transactions on, vol. 47, (2000), pp. 473-477.

- [2] M. Gravati, M. Valle, N. Guerrini and L. Reyes, "A novel current-mode very low power analog CMOS fourquadrant multiplier", In Proceedings of ESSCIRC, Grenoble, France, (2005).

- [3] A. Naderi, A. Khoei, K. Hadidi and H. Ghasemzadeh, "A new high speed and low power four-quadrant CMOS analog multiplier in current mode", AEU-International Journal of Electronics and Communications, vol. 63, (2009), pp. 769-775.

- [4] N. Beyraghi, A. Khoei and K. Hadidi, "CMOS design of a four-quadrant multiplier based on a novel squarer circuit", Analog Integrated Circuits and Signal Processing, vol. 80, (2014), pp. 473-481.

- [5] G. Colli and F. Montecchi, "Low-voltage low-power CMOS four-quadrant analog multiplier for neural network applications", International Symposium on Circuits and Systems, vol. 1, (1996), pp. 496–499.

- [6] W. Liu and S. I. Liu, "Design of a CMOS low-power and low-voltage four-quadrant analog multiplier", Analog Integrated Circuits and Signal Processing, vol. 63, (2010), pp. 307-312.

- [7] A. Pesavento and C. Kosh, "A wide linear range 4 quadrant multiplier in sub-threshold CMOS", International Symposium on Circuits and Systems, vol. 2, (1999), pp.240–243.

- [8] S. I. Liu and C. C. Chang, "CMOS sub-threshold four-quadrant multiplier based unbalanced source-coupled pair", International Journal of Electronics, vol. 78, (1992), pp.327–332.

- [9] L. S. Wong, "A very low-power CMOS mixed-signal IC for implantable pacemaker applications", Solid-State Circuits, IEEE Journal of, vol. 39, (2004), pp. 2446-2456.

- [10] G. Blakiewicz, "Analog multiplier for a low-power integrated image sensor", In 16th International Conference 'Mixed Design of Integrated Circuits and Systems, Loaz, Poland, June (2009).

- [11] J. N. Babanezhad and G. C. Temes, "A 20-V Four-Quadrant CMOS analog multiplier", IEEE Journal of Solid State Circuits, vol.20, (1985), pp.1158–1168.

- [12] Chen C. and Z. Li, "A low power CMOS analog multiplier", IEEE Transactions on Circuits and Systems-II: Express Briefs, vol.53, (2006), pp.100–104.

- [13] E. Ibaragi, A. Hyogo and K. Sekine, "A CMOS analog multiplier free from mobility reduction and body effect", Analog Integrated Circuits and Signal Processing, vol. 25, (2000), pp. 281–290.

- [14] A. Panigrahi and P. K. Paul, "A novel bulk-input low voltage and low power four-quadrant analog multiplier in weak inversion", Analog Integrated Circuits and Signal Processing, vol. 75, (**2013**), pp. 237-243.

- [15] R. R. Spencer, "Analog implementations of artificial neural networks, in Circuits and Systems", 1991, IEEE International Symposium on, (1991), pp. 1271-1274.

- [16] N. Saxena and J. J. Clark, "A four-quadrant CMOS analog multiplier for analog neural network", Solid-State Circuits, IEEE Journal of, vol. 29, (**1994**), pp. 746-749.

- [17] A. Rezai, P. Keshavarzi and R. Mahdiye, "A Novel MLP Network Implementation in CMOL Technology", Engineering Science and Technology, an International Journal (JESTECH), vol. 17, (2014), pp. 165–172.

- [18] B. Gilbert, "A precise four-quadrant multiplier with sub-nanosecond response, Solid-State Circuits", IEEE Journal of, vol. 3, (1968), pp. 365-373.

- [19] S. Sabeetha, J. Ajayan, S. Shriram, K. Vivek and V. Rajesh, "A study of performance comparison of digital multipliers using 22nm strained silicon technology, in Electronics and Communication Systems (ICECS)", 2015 2nd International Conference on, (2015), pp. 180-184.

- [20] K. Dejhan, P. Prommee, W. Tiamvorratat, S. Mitatha and I. Chaisayun, "A design of four-quadrant analog multiplier, in Communications and Information Technology, 2004. ISCIT 2004", IEEE International Symposium on, (2004), pp. 29-32.

- [21] C. Popa, "Improved accuracy current-mode multiplier circuits with applications in analog signal processing, Very Large Scale Integration (VLSI) Systems", IEEE Transactions on, vol. 22, (**2014**), pp. 443-447.

- [22] Y. P. Tsividis, "Operation and modeling of the MOS transistors", New York: oxford university publications, (2nd ed.), (2003), pp. 170-175.

- [23] M. J. Chen, J. S. Ho and D. Y. Chang, "Optimizing the match in weakly inverted MOSFET's by gated lateral bipolar action, Electron Devices", IEEE Transactions on, vol. 43, (1996), pp. 766-773.

- [24] E. A. Vittoz, "The design of high-performance analog circuits on digital CMOS chips", IEEE Journal of Solid-State Circuits, vol. 20, (1985), pp. 657-665.

- [25] M. J. Chen, "Dependence of current match on back-gate bias in weakly inverted MOS transistors and its modeling", Solid-State Circuits, IEEE Journal of, vol. 31, (1996), pp.259-262.

## Authors

**Sheema Soltany**, She is a student of higher education in Academic Center for Education, Culture and Research (ACECR) - Institute of higher education, Isfahan, Iran. She received B.S degree in Telecommunication engineering from Islamic Azad University, Najafabad, Isfahan, Iran in 2010. Her area of interests includes Analog IC designs, Low voltage and low power Analog circuits.

**Abdalhossein Rezai**, He is an assistant professor in Academic Center for Education, Culture and Research (ACECR), Isfahan University of Technology (IUT) branch, Isfahan, Iran. He received Ph.D. degree in electrical engineering from Semnan University, Semnan, Iran in 2013, M.S. and B.S. degree in electrical engineering from Isfahan University of Technology (IUT), Isfahan, Iran in 1999, and 2003, respectively. His research interests include network security, cryptography algorithm and its application, and neural network implementation in nanoelectronics.